I was recently looking at the page table architecture in x86 and x86-32 machines.

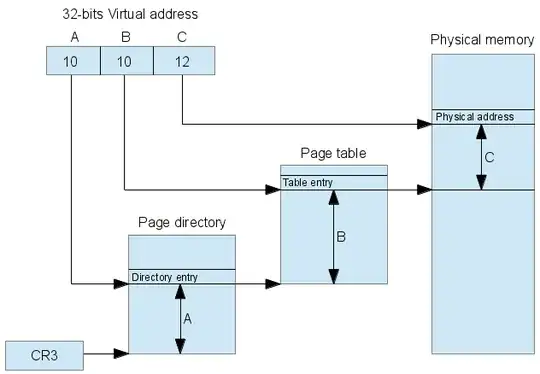

x86-32 paging architecture:

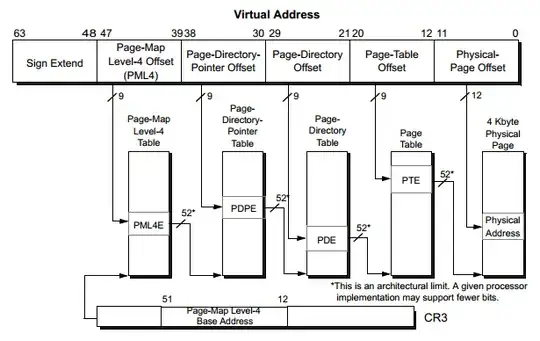

x86-64 paging architecture:

In x86 for example, we use 10 bits as offset into the page directory/page table. This means we can index 1K entries in a page directory/page table. But given that page directory and page table addresses have to be page aligned os's have to allocate 4K memory for page directories/tables

Is my understanding correct/ did I mess up the math somewhere.

If my understanding is correct, I have two followups

- If we have a lot of processes in a system( and thereby a lot of page directories and tables) isn't this a lot of wasted memory

- Are there any OS implementations that do interesting things with this 3k memory thats inaccessible